-

-

Notifications

You must be signed in to change notification settings - Fork 725

I2S sampling freq not correct for 8-bit @ 8 kHz #310

New issue

Have a question about this project? Sign up for a free GitHub account to open an issue and contact its maintainers and the community.

By clicking “Sign up for GitHub”, you agree to our terms of service and privacy statement. We’ll occasionally send you account related emails.

Already on GitHub? Sign in to your account

Comments

|

Hi @sandeepmistry , just bumping this to see if I can get a response, and I think you've been involved in the I2S stuff before. |

|

Please! Is anyone able to validate that this is a bug in the I2S library? |

|

Did you read the post! I didn't make modifications to the library. I added an extra call, in my own code, to the registers to change the frame sync bit width. And I didn't say changing sampling freqs didn't work, I clearly stated that changing word width from 16 bits to 8 bits caused problem. |

|

@sandeepmistry this is not closed. I try this code, and I get following result I haven't modifed library, I only changed bit width to 8 bits in I2S.begin |

|

@andrewjfox thanks for the sketch to reproduce, I can reproduce the problem with it. Calculations is too big to fit in the 8-bit divider value, so gets truncated to 119. If you use 8-bit @ 16kHz or 16-bit @ 8 kHz the issue does not occur. Just 8-bit @ 8 kHz |

|

Please provide your feedback on pull request #317 and let us know if it fixes the sketch from #310 (comment). Thanks. |

|

Yep, that's fixed it. Thanks for the quick reply. |

|

Closed via #317. |

Add int64_t and uint64_t data types to Serial.print(ln)

Hi,

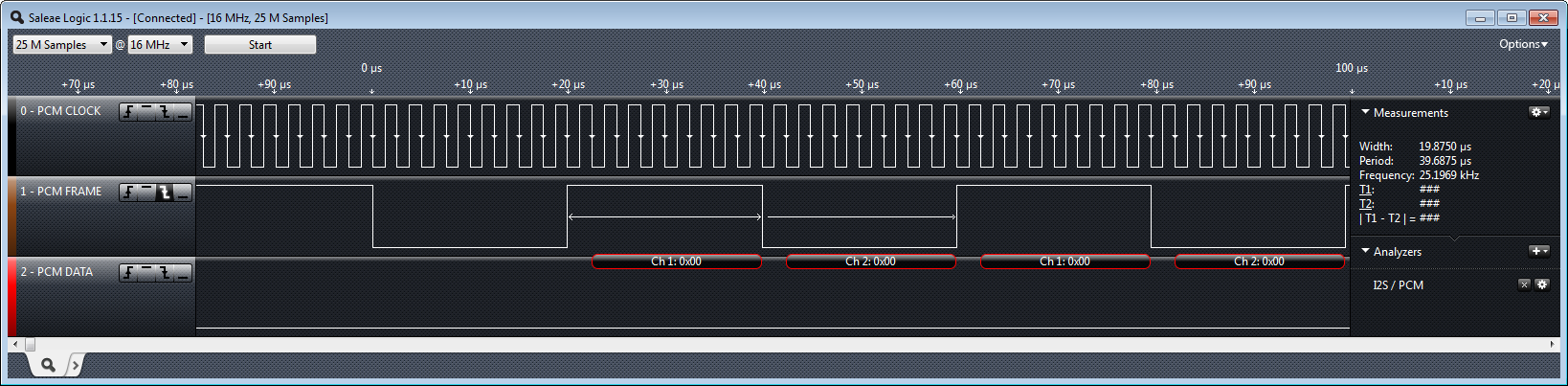

I've been trying to get audio from a modem using the I2S/PCM interface and having some troubles getting accurate clock frequencies.

I'm trying to read single 16bit words from modem @ 8kHz, by configuring the I2S as 8bit slots, since I see in the library it's expecting stereo so has min 2 slots. Following is code to init device, note that I am adjusting clock polarity and FS width to suit modem.

For this setup, with 8kHz sample rate I would expect SCLK to be 8000 * 2 * 8 = 128kHz, however when I monitor the I2S lines using logic analyser, the clock is around 400kHz, and FS is around 25kHz. See attached screen capture,

If I have it configured for 8kHz and 16bit data, then clock and frame are at 256kHz and 8kHz resepctively, as expected.

I had a look at the driver code but the clock setting is a bit complex at first glance so wasn't really able to locate where the issue is.

Regards

Andrew

The text was updated successfully, but these errors were encountered: